artnetv3

This is an old revision of the document!

Table of Contents

ArtNET Node v3

FPGA Register

Der FPGA enthält ein paar Register, die über den SPI Bus vom Microcontroller geschrieben/gelesen werden können. Mithilfe dieser Register werden alle Blöcke, die implementiert wurden, konfiguriert.

SPI Kommunikation

Register Schreiben

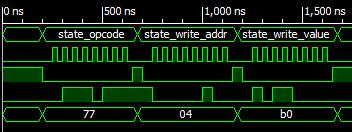

Um ein Register zu schreiben muss zuerst der Opcode 'w' (0x77) gesendet werden, dann die Registeradresse und zu Letzt der neue Wert.

Beispiel: Register 0x0B wird mit 0xB0 beschrieben

Registermap

| Address | Name | Description | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 0x00 | IPADDR0 | Lowest byte of IP address | interpreted as byte | |||||||

| 0x01 | IPADDR0 | … | interpreted as byte | |||||||

| 0x02 | IPADDR2 | … | interpreted as byte | |||||||

| 0x03 | IPADDR3 | Highest byte of IP address | interpreted as byte | |||||||

| 0x0C | IOACFG | config of physical I/O A | X | X | X | direction 0 = out, 1 = in | enable 0 = disabled, 1 = enabled | address of data buffer | ||

| 0x0C | IOBCFG | config of physical I/O B | X | X | X | direction | enable | address of data buffer | ||

| 0x0C | IOCCFG | config of physical I/O C | X | X | X | direction | enable | address of data buffer | ||

| 0x0C | IODCFG | config of physical I/O D | X | X | X | direction | enable | address of data buffer | ||

| 0x0C | IOECFG | config of physical I/O E | X | X | X | direction | enable | address of data buffer | ||

| 0x0C | IOFCFG | config of physical I/O F | X | X | X | direction | enable | address of data buffer | ||

| 0x0C | IOGCFG | config of physical I/O G | X | X | X | direction | enable | address of data buffer | ||

| 0x0C | IOHCFG | config of physical I/O H | X | X | X | direction | enable | address of data buffer | ||

artnetv3.1474733159.txt.gz · Last modified: by maxi2